移位寄存器及其应用实验报告总结,移位寄存器的工作原理

移位寄存器及其应用实验报告总结,移位寄存器的工作原理

移位寄存器及其应用实验报告总结。如果您的计算机没有安装windowsserver2003,请单击"下一步"。如果您的计算机安装了windowsserver2003,请单击"确定"。{1}{2}。{3}{4}。

一:移位寄存器及其应用实验报告总结

11.1寄存器

1、寄存器,就是能够记忆或存储0和1数码的基本部件。通常都是由各种触发器和门电路来构成的。

2、寄存器分为仅能存储0和1数码的数码寄存器,和既能存储数码同时也能实现数码的左移或右移的寄位移寄存器。

3、在实际中,通常使用集成寄存器。本节讲解了寄存器的电路构成、工作原理、对74LS194双向移位寄存器的使用进行了介绍。

(第1讲 寄存器)

1.1寄存器

1、寄存器:能够暂时存放数码、指令、运算结果的数字逻辑部件,称为寄存器。

2、寄存器电路如下:

寄存器电路

(1)由四个D触发器构成,因为每一个D触发器可以存放1位二进制信息,所以上述电路的寄存器可存放一个4位二进制数码,一般也把这种寄存器称为数码寄存器。

3、寄存器存放功能实现的过程:

寄存器各管脚定义

(1)电路中的CP是时钟控制端,也是寄存器的寄存指令控制端。 是直接清零端,通过 给各个触发器清零,在电路正常工作时, 置为高电位。 ~ 是数据输入端。 ~ 是数据输出端,

(2)假设要存储的二进制数码为1011,当 =1时,在控制寄存指令CP脉冲上升沿的作用下,根据D触发器的特性,输入端 ~ 的数码就一起送入了4各D触发器,输出端 、 、 此时置为1011,即完成了1011数码的寄存过程。

数码的寄存过程

总结:从这个寄存过程可以看出,寄存器在接受和输出数码信号时,各位数码都是同时打入到寄存器中的,输出端也即刻输出这组数码,这种输入输出的方式,称为并行输入、并行输出方式。

1.2左移寄存器

1、移位:在移位脉冲的作用下,每来一个时钟脉冲,寄存器数码便向右或向左移动一位,这种寄存器称为移位寄存器。

2、根据移位方式的不同,可分为单向移位寄存器、双向移位寄存器。

3、左移移位寄存器(单向)

左移移位寄存器

(1)D为数据输入端, ~ 为4个触发器,每个触发器的输入、输出依次相连, ~ 为数据输出端,CP为移位脉冲控制端, 为清零端。

(2)为简便分析,假设通过 端清零信号将4个触发器全部清零,而我们准备存储的数码为1011,首先,D=1,第一个移位脉冲上升沿到来时,触发器 置1,则 =1,其他触发器仍然保持0态。

第一个CP上升沿

(3)接着,D=0,第二个移位脉冲上升沿到来时,触发器 置1, 置0,则 =1, =0。

第二个CP上升沿

(4)再接着为D=1,第三个移位脉冲上升沿到来时,触发器 置1, 置0, 置1,则 =1, =0, =1。

第三个CP上升沿

(5)最后一个数据,D=1,第四个移位脉冲上升沿到来时,触发器 置1, 置0, 置1, 置1,则 =1, =0, =1, =1。

第四个CP上升沿

(6)在第四个移位脉冲过后,完成了存数过程,这时,从4个触发器的Q端,可以得到并行输出的信号。即经过4个脉冲后,1011这4位数码可以从 依次经历一边,此为串行输出。

1.2右移寄存器

1、右移寄存器:寄存器仍然由4个D触发器构成,与上面左移情况不同的是,串行数据是从 输入D端送入,触发器 的输出端接到 的输入端,依次类推。

右移寄存器

1.3双向移位寄存器

1、双向移位寄存器电路:既能实现左移,又能实现右移的寄存器。

(1)电路主要由4个D触发器构成,另外用与门和或门的组合来控制寄存器,来实现左移和右移的功能。

2、为了理解双向移位寄存器的工作过程,先分析移位触发器的情况:

移位触发器的情况

(1)要想实现数码的右移, = ;要想实现数码的左移, = ;

触发器的输入 = + ,

从这个逻辑式可以看出,当R=1,L=0时, = ,此时实现的是右移;当R=0,L=1时, = ,此时实现的是左移;

(2)将此分析过程应用到双向移位寄存器上,就可分析其左移和右移的过程了。

3、集成移位寄存器---74LS194四位双向移位寄存器

74LS194四位双向移位寄存器

(1) (1脚)数据清零端(低电平有效), ~ (3脚~6脚)并行数据输入端, ~ (12脚~15脚)并行数据输出端, (2脚)右移串行数据输入端, (7脚)左移串行数据输入端, 、 (9脚、10脚)为工作方式控制端, (11脚)时钟脉冲输入端,

(2)74LS194功能表

74LS194功能表

当 =0时,输出端清零;

当 =1, = =0时,输出端处于保持状态;

当 =1, =1, =0时,当时钟脉冲上升沿到来时,数据 ~ 依次进行右移,实现右移的功能;

当 =1, =0, =1时,当时钟脉冲上升沿到来时,数据 ~ 依次进行左移,实现左移的功能;

当 =1, = =1时,当时钟脉冲上升沿到来时,数据 ~ 并行接收数据端 ~ 的数据,实现并行输入的功能;

二:移位寄存器的工作原理

分别提供独立的时钟信号给移位寄存器和存储寄存器,移位寄存器具有直接清零功能和串行输入输出功能以及级联应用.(采用标准引脚。)移位寄存器和存储寄存器均为使用正边缘时钟触发,如果这两个时钟连接在一起,移位寄存器始终在存储寄存器的前一个时钟脉冲。

三:移位寄存器的功能

点击蓝字 ·

本文介绍一些verilog实现的数字电路的实例。如有错误,欢迎指出,感谢。

1

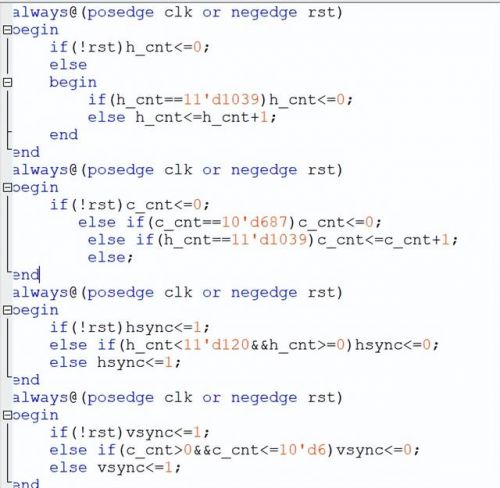

vga驱动

实验原理:VGA的显示效果取决于输入的RGB的值,R,G,B的值是通过不同的引脚接入的,逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

Experimental principle: VGA display effect depends on the input of the RGB values, R, G, B value is through different pin access, progressive scan is to scan from left upper corner of the screen, point by point scanning, from left as right after each scan line, electron beam back to the left of the screen to the next line of the starting position, during this period, the CRT to blanking of electron beam, at the end of each row, Synchronization with line synchronization signal; When all lines have been scanned, a frame is formed, the field sync signal is used for field sync, and the scan is returned to the upper left of the screen, and the field blanking is performed to start the next frame.

核心代码:

The core code:

波形:

wave:

2

数据接收端

实验原理:通过三个寄存器来判断上升沿和下降沿,当请求信号的上升沿出现时就开始启动接收数据当检测到下降沿时就接收数据完成,然后发送一个高脉冲给数据的发送端表示数据接收完毕。

Experimental principle: three registers are used to judge the rising edge and falling edge. When the rising edge of the request signal appears, it starts to receive data. When the falling edge is detected, the data is received, and then a high pulse is sent to the sender of data to indicate that the data is received.

RTL电路图:

RTL circuit diagram:

核心代码:

The core code:

波形:

wave:

3

UART发送12位数据

实验原理:使用状态机对状态进行切换,使用移位寄存器接收满了8位数据后就重新发送标志位,并重新开始接收。

Use the state machine to switch the state, use the shift register to receive full 8 bits of data on the re-send flag bits, and start receiving again.

核心代码:

The core code:

波形:

wave:

参考资料:

《FPGA/CPLD边学边练》吴厚航著

百度

翻译:谷歌翻译

四:移位寄存器左移和右移

可以通过左移和右移 *** 实现。

也可用并行的行送数法,并行送数法很简单只需把输入信号D1 D2 D3 D4为低电平就是哇。

左移抛弃最高位,低位填充的是0;右移抛弃最低位,高位补0;

-

- 东北酸汤子是啥_酸汤子是啥玩意

-

2023-09-28 14:58:43

-

- 梦见挤公交车好多人(梦见挤公交车挤不上去)

-

2023-09-28 14:56:28

-

- 劳动节的节日风俗(五一劳动节的节日风俗)

-

2023-09-28 14:54:13

-

- 本科一批省控是啥意思_本科一批省控线

-

2023-09-28 14:51:58

-

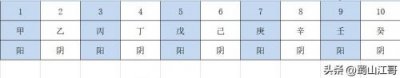

- 天干地支算法公式,月日时的天干地支算法

-

2023-09-28 14:49:43

-

- 父母婚礼贺词简短(父母婚礼贺词大全)

-

2023-09-28 14:47:28

-

- 率组词语和拼音(率组词语和拼音)

-

2023-09-28 14:45:13

-

- 化工技术转让网,化工技术转让平台

-

2023-09-28 14:42:58

-

- 苏州街地铁站16号线开通(苏州街地铁站10号线能换乘16号线吗)

-

2023-09-28 14:40:43

-

- 尼奥宠物站中国还能玩吗(尼奥宠物站 协会)

-

2023-09-28 14:38:29

-

- 索尼爱立信st15i版本低怎么办(索尼爱立信st15i无电池开机)

-

2023-09-28 08:18:13

-

- 重庆达内(重庆达内教育在哪里)

-

2023-09-28 08:15:58

-

- 面粉可以做什么好吃的?面粉可以做什么美食

-

2023-09-28 08:13:43

-

- 甲状腺低回声结节ti-rads3类_甲状腺低回声结节4a类什么意思

-

2023-09-28 08:11:28

-

- 山水田园水上乐园门票多少钱(山水田园水上乐园门票)

-

2023-09-28 08:09:13

-

- 淘宝网棒球服店铺推荐(淘宝棒球服哪家好)

-

2023-09-28 08:06:58

-

- 学校工作计划小学(学校工作计划2023年)

-

2023-09-28 08:04:43

-

- 河南二手车交易市场,河南二手车出口试点企业名单公示

-

2023-09-28 08:02:28

-

- 哈尔滨地图查询最新_哈尔滨市地图全图

-

2023-09-28 08:00:13

-

- 桃红柳绿的意思解释(桃红柳绿的意思和造句)

-

2023-09-28 07:57:58

70后退休工资一览表(70后最新退休年龄表)

70后退休工资一览表(70后最新退休年龄表) 今世缘等着我2023年最新一期(等着我今晚播出)

今世缘等着我2023年最新一期(等着我今晚播出)